题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

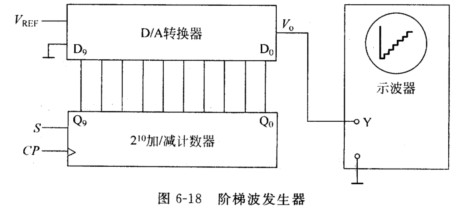

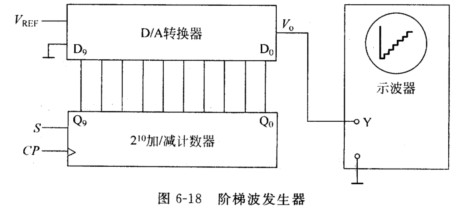

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1 MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1 MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

答案

答案

更多“图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),”相关的问题

更多“图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),”相关的问题

第1题

如图所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

第2题

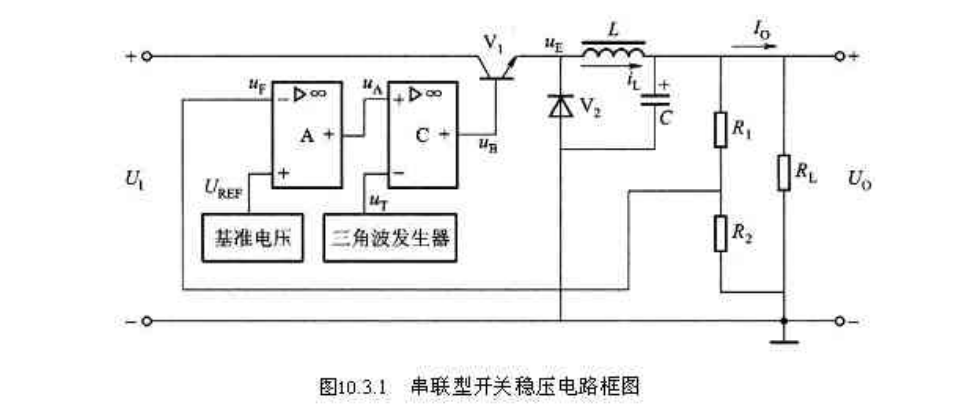

图10.3.1为串联开关稳压电路的基本组成框图。图中V1为开关元件调整管,V2为续流二极管L、C构成L型滤波电路,R1和R2组成取样电路、A 为误差放大、C为电压比较器它们与基准电压、三角波发生器组成开关调整管的控制电路。取样电压UF 、基准电压UREF、三角波电压UT。UT决定着电源开关的频率。比较器的输出uB控制着调整管的导通和截止。uB、UT、UA的波形如图8.3.2(a)、(b)

第3题

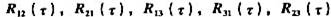

以图6-18所示k=1,2,3的三个沃尔什函数作为CDMA系统的地址码 .分别求它们的自相关函数

.分别求它们的自相关函数 以及互相关函数

以及互相关函数

(粗略画图形即可).由所得结果讨论此码组是否能用作地址码.

(粗略画图形即可).由所得结果讨论此码组是否能用作地址码.

第4题

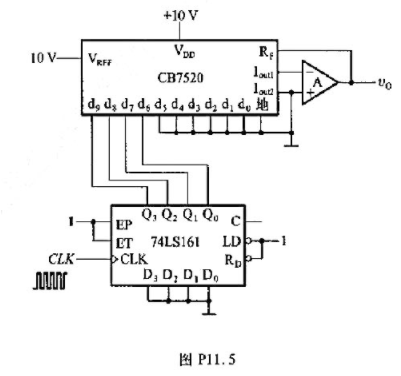

图10.4.1所示电路是用十位集成R-2R倒T型数模转换器CB7520和74LS161组成的波形发生器电路。已知CB7520参考电压VREF=-10 V,请求出vO的值,CB7520的电路结构如图10.3.2所示。

1.jpg)

第5题

图P11.5所示电路是用CB7520和同步十六进制计数器74LS161组成的波形发生器电路.已知CB7520的 ,试画出输出电压v0的波形,并标出波形图上各点电压的幅度.

,试画出输出电压v0的波形,并标出波形图上各点电压的幅度.

第7题

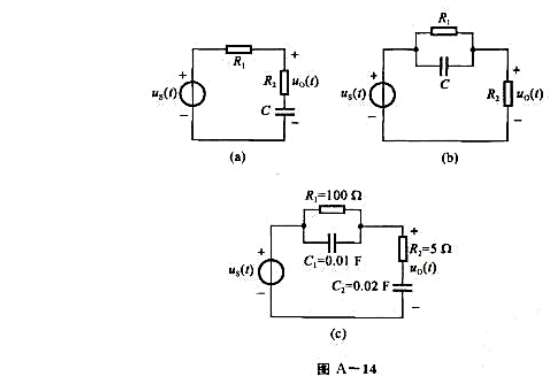

图所示电路是低频信号发生器中常用的一种电路,称为R-C选频网络。当输入电压

第8题

电压u1(t)的ω值。