题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

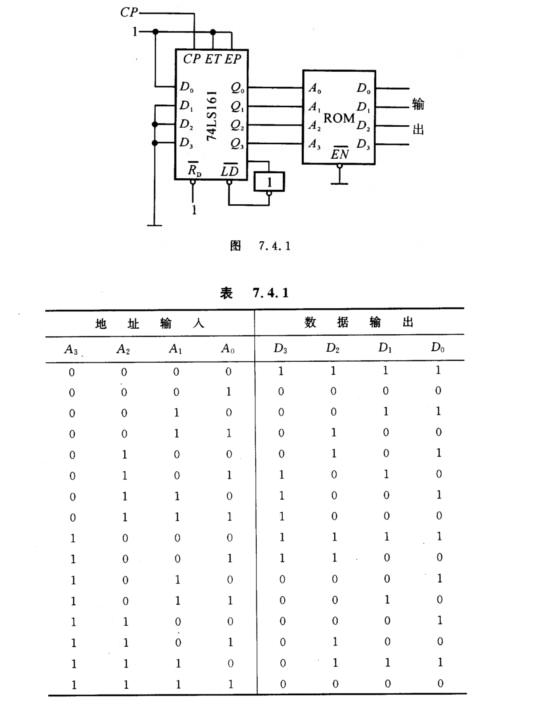

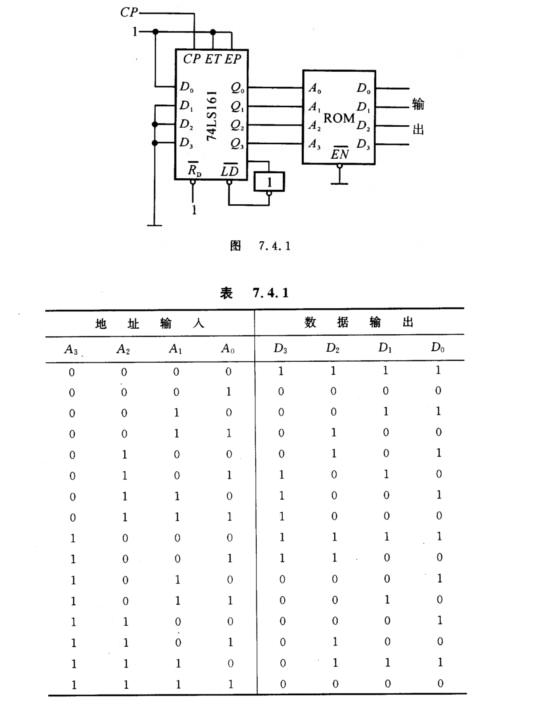

如图7.4.1所示为用16×4位ROM和同步十六进制加法计数器74LSl61组成的脉冲分频电路,ROM的数据表如

表7.4.1所示。求出在CP信号连续作用下D3~D0的输出序列,并说明它们与CP信号频率之比。

答案

答案

查看答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“如图7.4.1所示为用16×4位ROM和同步十六进制加法计数器74LSl61组成的脉冲分频电路,ROM的数据表如”相关的问题

更多“如图7.4.1所示为用16×4位ROM和同步十六进制加法计数器74LSl61组成的脉冲分频电路,ROM的数据表如”相关的问题

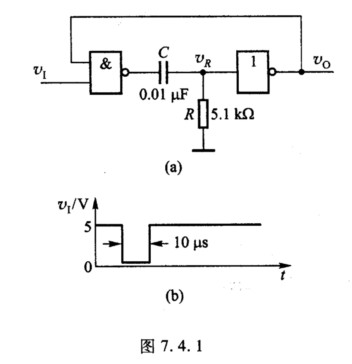

第3题

(1)试分析电路的工作原理,该电路是什么电路? (2)画出vR及vO的波形,计算输出脉冲宽度及最高工作频率。

(1)试分析电路的工作原理,该电路是什么电路? (2)画出vR及vO的波形,计算输出脉冲宽度及最高工作频率。

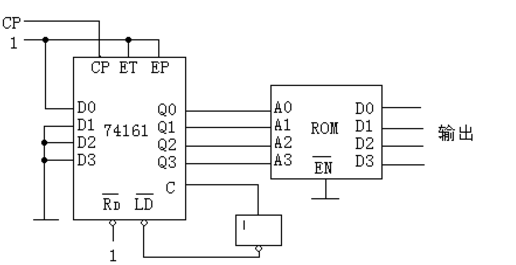

第4题

号连续作用下D3、D2、D1、D0输出的电压波形,并说明它们和CP信号频率之比。

| 地址输入 | 数据输出 |

| A3A2A1A0 | D3D2D1D0 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 1 1 1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 0 1 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 1 0 0 0 0 0 1 0 0 1 0 0 0 0 1 0 1 0 0 0 1 1 1 0 0 0 0 |

第5题

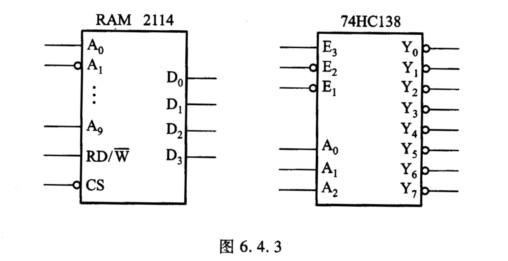

RAM 2114芯片(容量为1 K×4位)和3线-8线译码器74HCl38的简化框图如图6.4.3所示,试用这两种类型的芯片组成4 K×8位的存储器系统,写出设计思想,画出逻辑图。

第6题

第8题

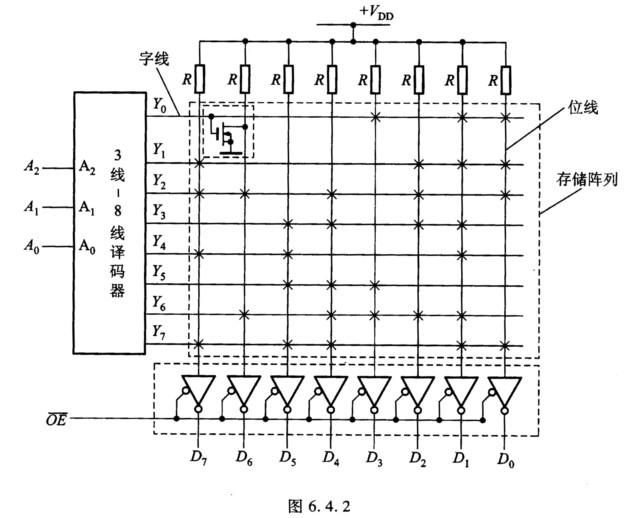

(1)若地址译码器的输入A2A1A0取值为000、001、010、…、111时,其相应的输出Y0、Y1、Y2、…、Y7为高电平。试问输入A2A1A为010、011、101时,ROM相应的输出状态是什么? (2)若已知ROM的输出为10110011,试问地址译码器的输入A2A1A0应该是什么状态?

(1)若地址译码器的输入A2A1A0取值为000、001、010、…、111时,其相应的输出Y0、Y1、Y2、…、Y7为高电平。试问输入A2A1A为010、011、101时,ROM相应的输出状态是什么? (2)若已知ROM的输出为10110011,试问地址译码器的输入A2A1A0应该是什么状态?

第9题

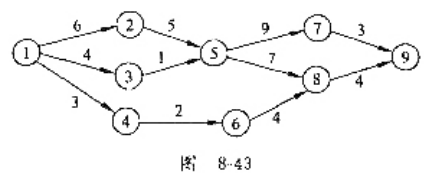

在如图B-43所示的AOE网中,关键路径长度为()。

A、23

B、22

C、16

D、13