题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

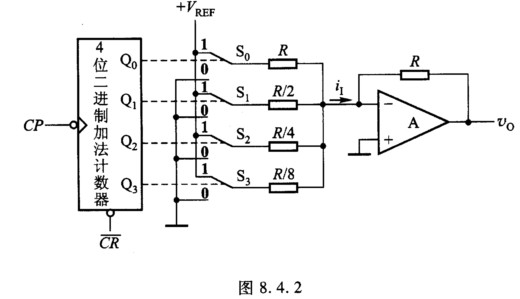

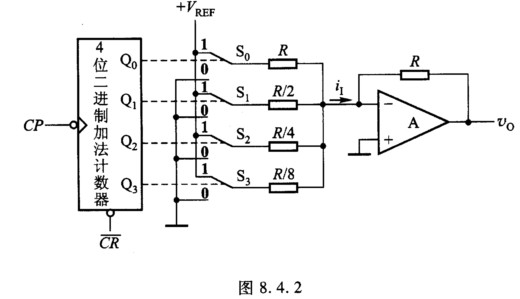

某D/A转换器逻辑图如图8.4.2所示,图中Qi=l时,相应模拟开关Si在位置1。Qi=O时,开关Si在位置0。

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“某D/A转换器逻辑图如图8.4.2所示,图中Qi=l时,相应模拟开关Si在位置1。Qi=O时,开关Si在位置0。”相关的问题

更多“某D/A转换器逻辑图如图8.4.2所示,图中Qi=l时,相应模拟开关Si在位置1。Qi=O时,开关Si在位置0。”相关的问题

第2题

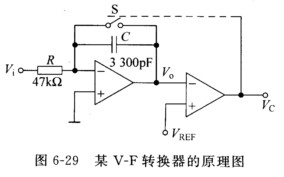

某V-F转换器的原理图如图6-29所示。已知Vi=10V,VREF=-6V,试求: (1)画出变换过程中Vo,VC的波形(忽略C 的放电时间); (2)估算输出脉冲VC的频率; (3)若Vj改为4.5V,则VC的频率变为多少?

第3题

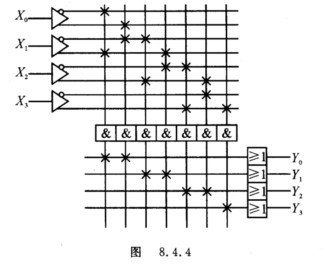

已知4输入/4输出FPLA器件的映象逻辑图如图8.4.4所示,试写出其逻辑函数输出表达式。

第7题

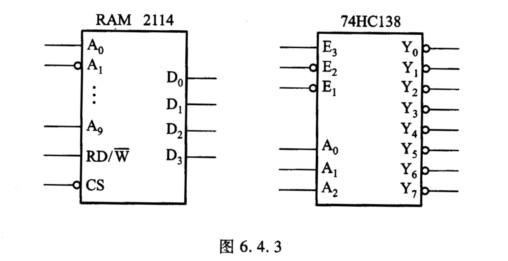

RAM 2114芯片(容量为1 K×4位)和3线-8线译码器74HCl38的简化框图如图6.4.3所示,试用这两种类型的芯片组成4 K×8位的存储器系统,写出设计思想,画出逻辑图。

第8题

74LS293型计数器的逻辑图、外引线排列图及功能表如图21-39所示。它有两个时钟脉冲输入端CP0和CP1。试问(1)从CP0输入,Q0输出时,是几进制计数器?(2)从CP1输入,Q3,Q2,Q1输出时,是几进制计数器?(3)将Q0端接到CP1端,从CP0输入,Q3,Q2,Q1,Q0输出时,是几进制计数器?图中R0(1)和R0(2)是清零输入端,当该两端全为1时,将四个触发器清零。

第9题

在如图8.1.2所示倒T形电阻网络D/A转换器中,已知Rf=R=10 kΩ, VREF=10 V。试求 (1)vO的输出范围; (2)当D3D2D1D0=0110时,vO=?

.jpg)

第10题

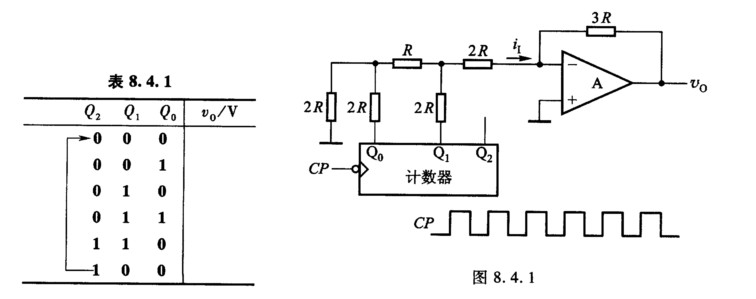

一个R-2R梯形网络D/A转换器如图8.4.1所示,图中计数器的初始状态Q2Q1Q=000,输出端高电平为8 V,低电平为0 V,计数器状态表如表8.4.1所示。将计数器各状态下D/A转换器的输出电压vO值填入表8.4.1中;并画出与CP对应的输出vO波形。