题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

存储芯片中包括存储体、读写电路、地址译码电路和控制电路()。

存储芯片中包括存储体、读写电路、地址译码电路和控制电路()。

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

存储芯片中包括存储体、读写电路、地址译码电路和控制电路()。

答案

答案

更多“存储芯片中包括存储体、读写电路、地址译码电路和控制电路()。”相关的问题

更多“存储芯片中包括存储体、读写电路、地址译码电路和控制电路()。”相关的问题

第1题

A.主存的读写时钟频率

B.主存的容量和编址模式

C.是否使用多体交叉结构

D.采用具体存储芯片的个数

E.采用全地址译码还是部分地址译码

第2题

若用74138译码片选4片2K×8存储器芯片,

第3题

若用74LS138译码片选4片2K×8存储器芯片,P2.3、P2.4、P2.5接A,B,C,G1接Vcc,P2.6接 接地,试画出其连接电路,指出4片存储芯片的地址范围(无关位为1)。

接地,试画出其连接电路,指出4片存储芯片的地址范围(无关位为1)。

第6题

在使用译码器同时扩展多片RAM芯片时,不能在各存储芯片间并行连接的信号是()。

A.读写信号

B.地址译码器输出信号

C.输入/输出数据信号

D.高位地址信号

第7题

设某微机的寻址范围为64K,接有8片8K的存储芯片,存储芯片的片选信号为CS,要求: (1)画出选片译码逻辑电路(可选用74138译码器)。 (2)写出每片RAM的地址范围。 (3)如果运行时发现只有以0000H为起始地址的一片存储芯片不能读/写,分析故障原因,如何解决? (4)如果发现只能对第1~4片RAM进行读/写,试分析故障原因。

第8题

第9题

某计算机的主存地址空间中,从地址0000H~3FFFH为ROM存储区域,从地址

4000H~7FFFH为RAM的存储区域。RAM的控制信号为CS和WE,CPU的地址线为A15~A0,数据线为8位的D7~D0线,控制信号有读写控制R/W和访存请求MREQ,要求: (1)画出地址译码方案。 (2)如果ROM和RAM存储器芯片都采用8 K×1位的芯片,试画出存储器与CPU的连接图。 (3)如果ROM存储器芯片采用8K×8位的芯片,RAM存储器芯片采用4K×8位的芯片, 试画出存储器与CPU的连接图。 (4)如果ROM存储器芯片采用16K×8位的芯片,RAM存储器芯片采用8K×8位的芯片,试画出存储器与CPU的连接图。

4000H~7FFFH为RAM的存储区域。RAM的控制信号为CS和WE,CPU的地址线为A15~A0,数据线为8位的D7~D0线,控制信号有读写控制R/W和访存请求MREQ,要求: (1)画出地址译码方案。 (2)如果ROM和RAM存储器芯片都采用8 K×1位的芯片,试画出存储器与CPU的连接图。 (3)如果ROM存储器芯片采用8K×8位的芯片,RAM存储器芯片采用4K×8位的芯片, 试画出存储器与CPU的连接图。 (4)如果ROM存储器芯片采用16K×8位的芯片,RAM存储器芯片采用8K×8位的芯片,试画出存储器与CPU的连接图。

第10题

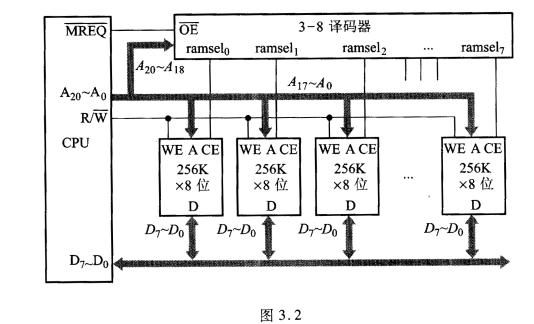

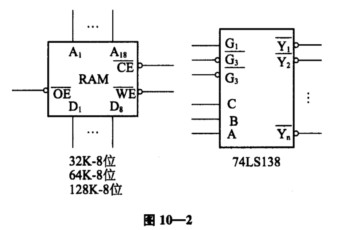

设CPU有18根地址线和8根数据线,并用IO/M(M取反)作访存控制信号,R/W(W取反)作读写命令,存储器采用四体低位交叉结构,画出CPU和存储芯片的连接图(见图10—2)。 要求: (1)合理选用下列芯片,门电路自定。 (2)写出每片存储芯片的二进制地址范围。 (3)详细画出存储芯片的片选逻辑。 (4)该存储器在一个存取周期内可向CPU提供多少位信息?

第11题

电平为读,低电平为写)。现有下列存储芯片:1K×4位RAM,4K×8位RAM,2K×8位ROM,以及74138译码器和各种门电路,如图所示。画出CPU与存储器连接图,要求:1.主存地址空间分配:8000H~87FFH为系统程序区;8800H~8BFFH为用户程序区。

2.合理选用上述存储芯片,说明各选几片?

3.详细画出存储芯片的片选逻辑。