题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

在CPU的寄存器中,PC表示______寄存器;SP表示______寄存器。

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“在CPU的寄存器中,PC表示______寄存器;SP表示______寄存器。”相关的问题

更多“在CPU的寄存器中,PC表示______寄存器;SP表示______寄存器。”相关的问题

第1题

A、DR、AR、PC、IR

B、DR、PC、IR、AR

C、DR、IR、AR、PC

D、AR、IR、DR、PC

第2题

(31)

A. DR,IR,AR,PC

B. IR,AR,PC,DR

C. AR,PC,DR,IR

D. PC,DR,IR,AR

第3题

A.增加CPU中寄存器的个数

B.提高CPU的主频

C.增加高速缓存(Cache)的容量

D.优化BIOS的设计

第6题

A.为了暂存中间结果,CPU中包含几十个甚至上百个寄存器,用来临时存储数据

B.CP间PC机中不可缺少的部件,它担负着运行系统软件和应用软件的任务

C.所有PC机的CPU都具有相同的指令系统

D.一台计算机至少必须包含一个CPU,也可能包含2个,4个,8个甚至更多个CPU

第7题

A.为了暂存中间结果,CPU中包含几十个甚至上百个寄存器,用来临时存放数据

B.CPU是PC中不可缺少的组成部分,它担负着运行系统软件和应用软件的任务

C.所有PC的CPU都具有相同的机器指令

D.CPU至少包含1个处理器,为了提高计算速度,CPU也可以由2个、4个、8个甚至更多个处理器组成

第8题

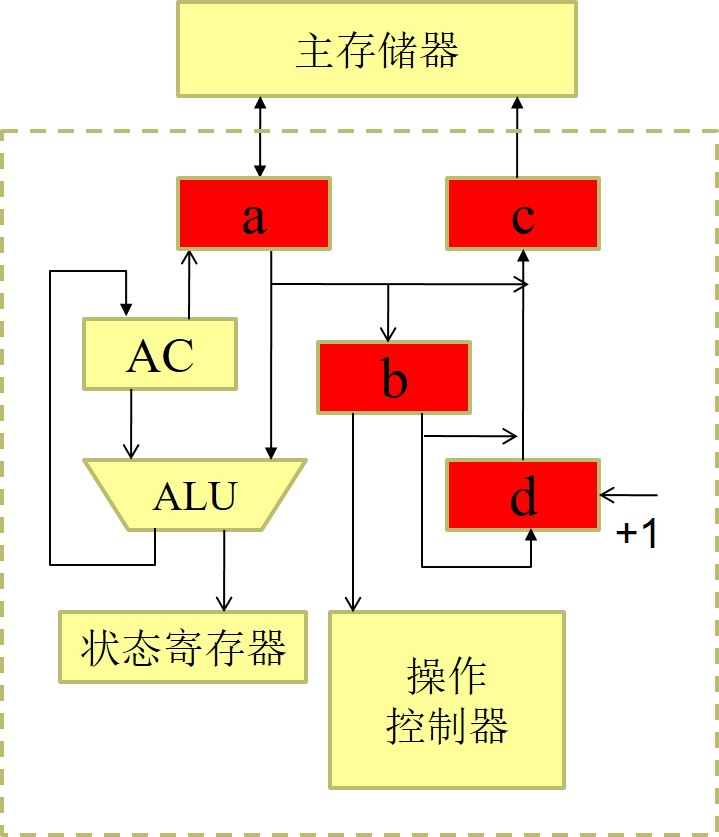

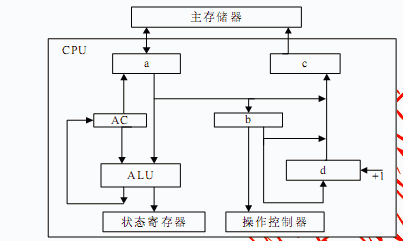

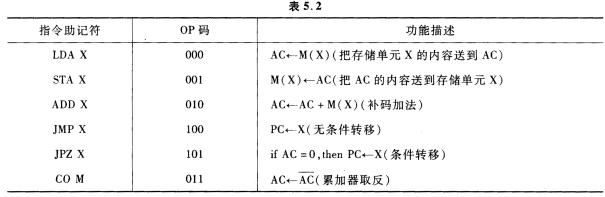

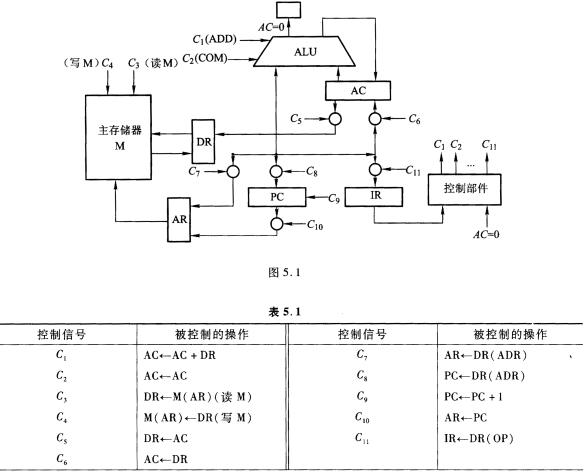

CPU的结构如图5.1所示,其中AC为累加器,AR为主存地址寄存器,DR为主存数据寄存器,DR(OP)为DR的操作码字段,DR(ADR)为DR的地址码字段,IR为指令寄存器,Pc为程序计数器。M为主存储器。表5.1列出CPU控制信号,表5.2列出指令组助记符及其功能,并给出每条指令的操作码。

试设计:(1)满足所给条件的微指令格式(直接控制法)。 (2)设计表5?2中6条指令的微程序流程图,标明每条微指令在控制存储器中的地址。

试设计:(1)满足所给条件的微指令格式(直接控制法)。 (2)设计表5?2中6条指令的微程序流程图,标明每条微指令在控制存储器中的地址。

第9题

在关于微处理器的叙述中,不正确的是( )。

A)它由单片大规模集成电路制成,具有运算、控制和存储功能

B)它包含几十个甚至上百个“寄存器”,用来临时存放正在处理的数据

C)PC机中的微处理器只有1个,它就是CPU

D)美国Intel公司是国际上研究、开发和生产微处理器最有名的公司

第10题