题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

某机器采用四体低位交叉存储器,现分别执行下述操作:①读取6个连续地址单元中存放的存储字,重复80

A.1:1

B.2:1

C.4:3

D.3:4

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.1:1

B.2:1

C.4:3

D.3:4

答案

答案

更多“某机器采用四体低位交叉存储器,现分别执行下述操作:①读取6个连续地址单元中存放的存储字,重复80”相关的问题

更多“某机器采用四体低位交叉存储器,现分别执行下述操作:①读取6个连续地址单元中存放的存储字,重复80”相关的问题

第1题

A.在0.1 μs内,存储器可向CPU提供26位二进制信息

B.在0.1 μs内,每个体可向CPU提供16位二进制信息

C.在0.4 μs内,存储器可向CPU提供26位二进制信息

第2题

设X、Y、Z均为n+1位寄存器(n为最低位),机器数采用1位符号位。若除法开始时操作数已放在合适的位置,试分别描述原码和补码除法商符的形成过程。

第4题

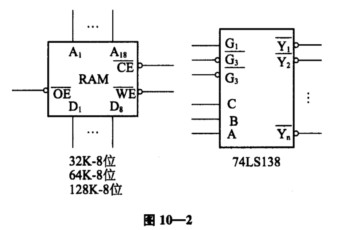

设CPU有18根地址线和8根数据线,并用IO/M(M取反)作访存控制信号,R/W(W取反)作读写命令,存储器采用四体低位交叉结构,画出CPU和存储芯片的连接图(见图10—2)。 要求: (1)合理选用下列芯片,门电路自定。 (2)写出每片存储芯片的二进制地址范围。 (3)详细画出存储芯片的片选逻辑。 (4)该存储器在一个存取周期内可向CPU提供多少位信息?

第5题

第6题

某小数定点机,字长8位(含1位符号位),当机器数分别采用原码、补码和反码时,其对应的真值范围分别是________、________、________(均用十进制表示)。

第7题

某整数定点机,字长8位(含1位符号位),当机器数分别采用原码、补码、反码及无符号数时,其对应的真值范围分别为________、________、________和________(均用十进制数表示)。

第8题

第9题

某计算机的主存采用体宽为8B的8体交叉存储器,数据总线的宽度为64位,读一个主存块的步骤: (1)发送首地址到主存(一个总线时钟周期); (2)主存控制器接受到地址后,启动第一个模块准备数据,并每隔一个总线时钟启动下一个模块准备数据。每个存储模块花4个总线时钟准备好64位数据,总线上传输一个64位数据花一个总线时钟。请问: 该计算机的Cache缺失损失(从主存中读一个主存块到Cache的时间)至少为多少总线时钟周期?

第10题

在补码一位乘法中,设[x]补为被乘数,[y]补为乘数,若ynyn+1(yn+1为低位)=00,应执行________操作,若ynyn+1=01,应执行________操作,若ynyn+1=10,应执行________操作,若ynyn+1=11,应执行________操作。若机器数字长为16位(不包括符号位),则补码乘法需做________次________操作,最多需做________次________操作。