题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

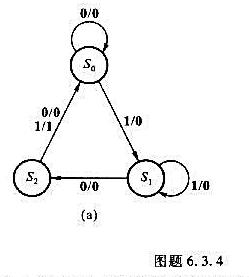

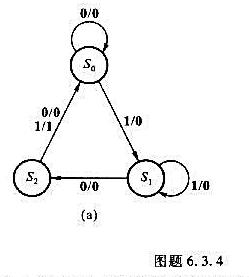

试用下降沿出发的D触发器设计一同步时序电路,状态图如6.3.4(a),S0,S1,S2的编码如6

试用下降沿出发的D触发器设计一同步时序电路,状态图如6.3.4(a),S0,S1,S2的编码如6

.3.4(a)。

答案

答案

查看答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

.3.4(a)。

答案

答案

更多“试用下降沿出发的D触发器设计一同步时序电路,状态图如6.3.4(a),S0,S1,S2的编码如6”相关的问题

更多“试用下降沿出发的D触发器设计一同步时序电路,状态图如6.3.4(a),S0,S1,S2的编码如6”相关的问题

第1题

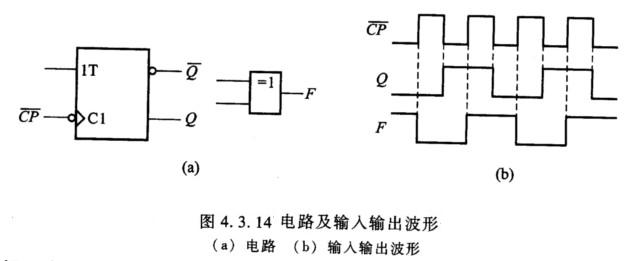

试用图4.3.14(a)给定的触发器和逻辑门设计波形产生电路。要求图(a)中的各信号满足图4.3.14(b)所示时序关系。

第3题

第4题

同步时序逻辑电路与异步时序逻辑电路的不同之处在于后者()。

A.没有触发器

B.没有统一的时钟脉冲控制

C.没有稳定状态

D.输出只与内部状态有关

第7题

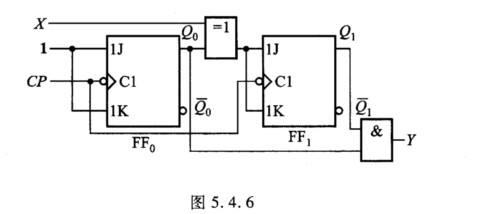

试用同步时序电路分析方法分析图5.4.6所示电路,画出状态图和波形图,确定电路的逻辑功能(设触发器的初始状态均为0)。

第11题

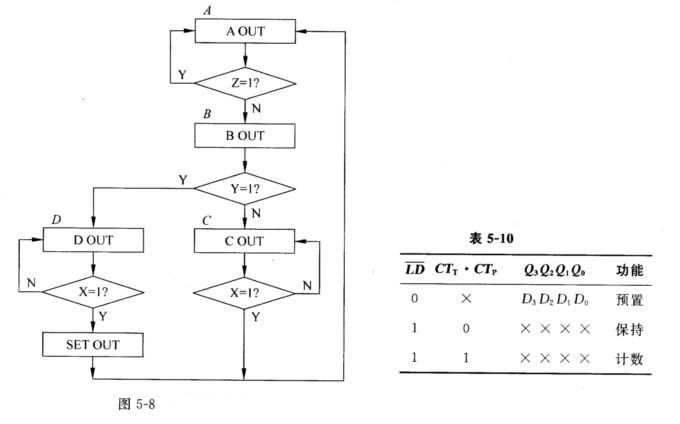

用MSI时序模块实现同步时序电路。 某系统ASM图如图5-8所示,试设计该图描述的控制器(条件输出块和状态块中所标符号为输出信号)。要求用集成计数器74LS163为核心进行设计。(附74LS163计数器主要功能表,如表5-10所示。)