题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

OD门,即集电极开路门电路;OC门,即漏极开路门电路()

答案

答案

否

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

否

更多“OD门,即集电极开路门电路;OC门,即漏极开路门电路()”相关的问题

更多“OD门,即集电极开路门电路;OC门,即漏极开路门电路()”相关的问题

第3题

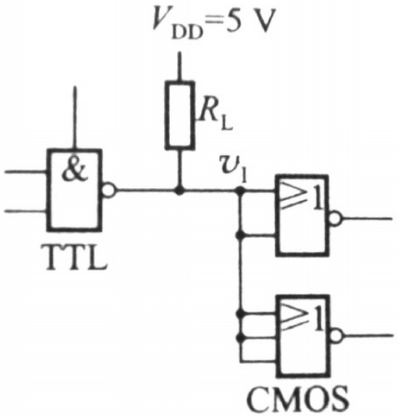

图是用TTL输出开路门(OC门)电路驱动CMOS电路的实例,试计算上拉电阻RL的取值范围。TTL输出开路与非门在VOL≤0.3V时的最大输出电流为8mA,输出端的VT5晶体管截止时有50μA的漏电流。CMOS或非门的输入电流可以忽略。要求加到CMOS或非门输入端的电压满足VIH≥4V,VIL≤0.3V。给定电源电压VDD=5V。

第4题

电路如图2.4.16(a)所示。已知当三极管导通时Vbe=0.7V,饱和时Vces=0.3V,β=100;OC门G1输出管截止时的漏电流约为50μA,饱和导通时最大允许灌电流ILM=10mA,输出低电平VOL=0.3V;TTL与非门输入特性如图(b)所示。要求三极管集电极输出端P为高电平时VPH=3.5V,低电平时VPL=0.3V。试问:

第10题

第11题

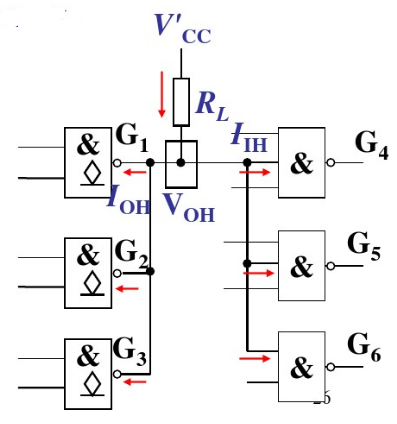

计算图3.23电路中上拉电阻RL的阻值范围。其中,G1、G2、G3是74LS系列OC门,输出管截止时的漏电流IOH≤100μA,输出低电平VOL≤0.4V时允许的最大负载电流IOLmax=8mA。G4、G5、G6为74LS系列与非门,它们的输入电流为|IIL|≤0.4mA、IOH≤20μA。给定VCC=5 V,要求OC门的输出高、低电平应满足VOH≥3.2V、VOL≤0.4V。