题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

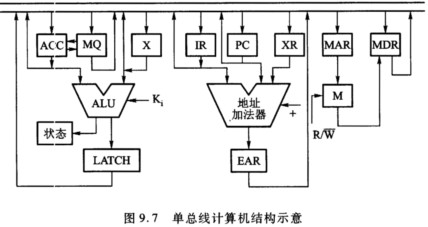

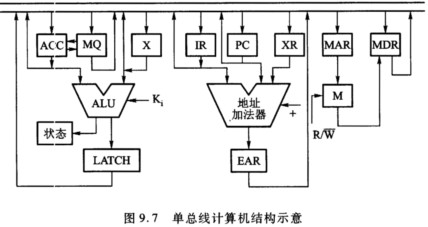

已知单总线计算机结构如图9.7所示,其中M为主存,XR为变址寄存器,EAR为有效地址寄存器,LATCH为暂存

说明: (1)ADD X,D指令字中x为变址寄存器XR,D为形式地址。 (2)寄存器的输入和输出均受控制信号控制,如PCi表示PC的输入控制信号,又如MDRo表示MDR的输出控制信号。 (3)凡是需要经过总线实现寄存器之间的传送,需在流程图中注明,如PC→Bus→MAR,相应的控制信号为PCo和MARi。

说明: (1)ADD X,D指令字中x为变址寄存器XR,D为形式地址。 (2)寄存器的输入和输出均受控制信号控制,如PCi表示PC的输入控制信号,又如MDRo表示MDR的输出控制信号。 (3)凡是需要经过总线实现寄存器之间的传送,需在流程图中注明,如PC→Bus→MAR,相应的控制信号为PCo和MARi。

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

说明: (1)ADD X,D指令字中x为变址寄存器XR,D为形式地址。 (2)寄存器的输入和输出均受控制信号控制,如PCi表示PC的输入控制信号,又如MDRo表示MDR的输出控制信号。 (3)凡是需要经过总线实现寄存器之间的传送,需在流程图中注明,如PC→Bus→MAR,相应的控制信号为PCo和MARi。

说明: (1)ADD X,D指令字中x为变址寄存器XR,D为形式地址。 (2)寄存器的输入和输出均受控制信号控制,如PCi表示PC的输入控制信号,又如MDRo表示MDR的输出控制信号。 (3)凡是需要经过总线实现寄存器之间的传送,需在流程图中注明,如PC→Bus→MAR,相应的控制信号为PCo和MARi。

答案

答案

更多“已知单总线计算机结构如图9.7所示,其中M为主存,XR为变址寄存器,EAR为有效地址寄存器,LATCH为暂存”相关的问题

更多“已知单总线计算机结构如图9.7所示,其中M为主存,XR为变址寄存器,EAR为有效地址寄存器,LATCH为暂存”相关的问题

第1题

第2题

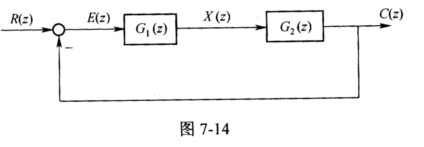

已知离散系统结构如图7-14所示。

其中:x(k)=x(k)-x(k-1),c(k)=1.5c(k-1)-5c(k-2)+4x(k-1)。试确定系统的脉冲传递函数G1(z)和G2(z)并判断系统的稳定性。

其中:x(k)=x(k)-x(k-1),c(k)=1.5c(k-1)-5c(k-2)+4x(k-1)。试确定系统的脉冲传递函数G1(z)和G2(z)并判断系统的稳定性。

第3题

高电平为读,低电平为写)。

已知该机存储器地址空间从0连续编址,其地址空间分配如下:最低8K为系统程序区,由ROM芯片组成;紧接着40K为备用区,暂不连接芯片;而后78K为用户程序和数据空间,用静态RAM芯片组成;最后2K用于I/O设备(与主存统一编址)。现有芯片如下:

SRAM:16K×8位,其中CS:为片选信号,低电平有效,WE:为写控制信号,低电平写,高电平读。

ROM:8K×8位,其中CS:为片选信号,低电平有效,OE:为读出控制,低电平读出有效。

译码器:3―8译码器,输出低电平有效;为使能信号,低电平时译码器功能有效。

其它“与、或”等逻辑门电路自选。

(1)请问该主存需多少SRAM芯片?

(2)试画出主存芯片与CPU的连接逻辑图。

(3)写出各芯片地址分配表。

第5题

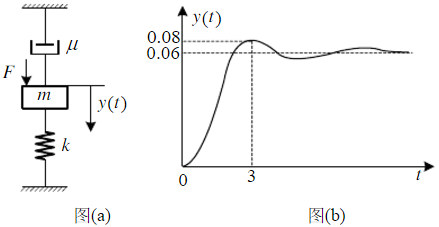

已知质量-弹簧-阻尼器系统如图(a)所示,其中质量为mkg,弹簧系数为kN/m,阻尼器系数为μN·s/m,当物体受F=10N的恒力作用时,其位移y(t)的变化如图(b)所示。求m、k和μ的值。

第6题

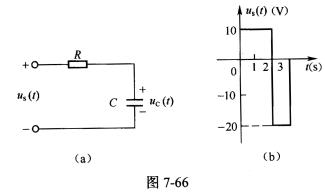

图7.66(a)所示的RC电路,已知uc(0-)=0,t>0时所加电压us(t)的波形如图7.66(b)所示,其中R=1000Ω,C=10uF。试求t>0时的电容电压uc(t)。

第7题

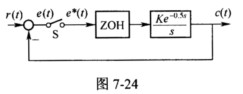

已知离散系统如图7-24所示。

其中:ZOH为零阶保持器,T=0.25s,当r(t)=2+t时,欲使稳态误差小于0.1,试求K值。

其中:ZOH为零阶保持器,T=0.25s,当r(t)=2+t时,欲使稳态误差小于0.1,试求K值。

第8题

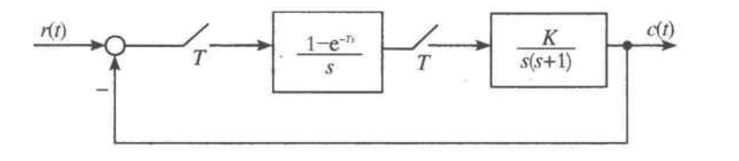

已知采样系统如图7-16所示,其中T=1s,K=1,

试求:

(1)闭环脉冲传递函数。

(2)判断系统是否稳定。

(3)写出描述系统教学模型的差分方程。

第9题

理想气体经历如图4—6所示循环,其中bc和da为绝热过程。已知Tc=300K,T6=400K。求按此循环工作的热机的效率。